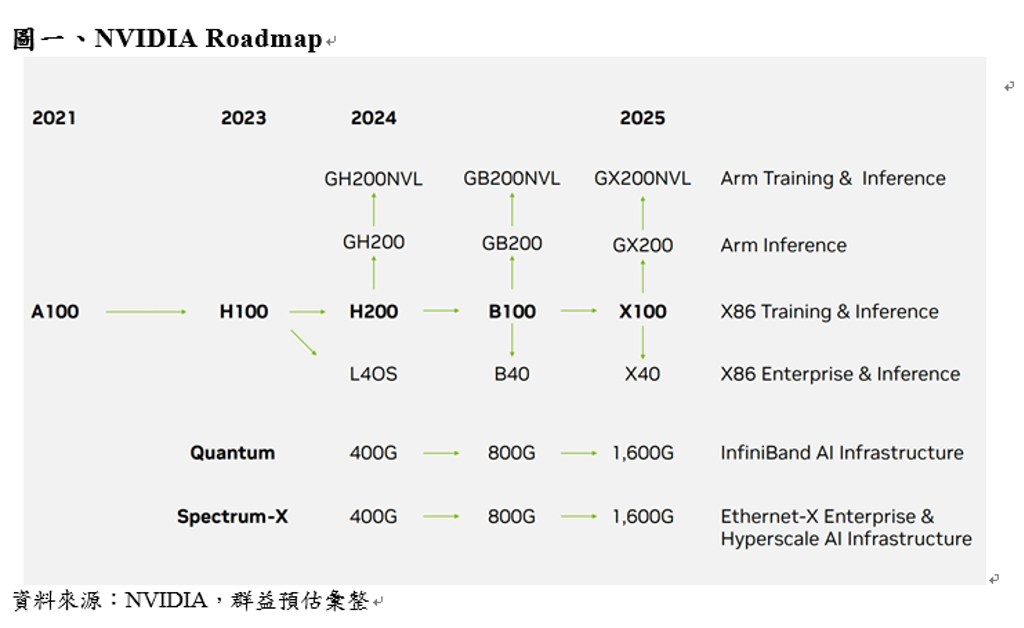

NVIDIA(NVDA US)正式發佈號稱迄今最強AI晶片架構GB200。受惠AI紅利,台積電(2330TT)2024年在N5/N3製程和先進封裝CoWoS帶動下,營運動能佳。

NVIDIA正式發布號稱迄今最強AI晶片架構GB200:

NVIDIA GTC(GPU Technology Conference)大會於美西時間2024/3/18登場,正式發布號稱迄今最強AI晶片架構GB200,並計畫於2024年晚些正式出貨,GB200為採用新一代Blackwell架構GPU,Blackwell架構的AI晶片性能將更加強大,更擅長處理AI相關的任務。而Blackwell架構則是以數學家David Harold Blackwell的名字命名。

Blackwell架構GPU的AI運算性能在FP8及NEW FP6上都可達20petaflops,是前一代Hopper架構運算性能8petaflops的2.5倍。在NEW FP4上更可達到40petaflops,是前一代Hopper架構GPU運算性能8petaflops的5倍。而取決於各種Blackwell架構GPU設備的記憶體容量和頻寬配置,工作運算執行力的實際性能可能會更高。黃仁勳強調,有了這些額外的處理能力,將使人工智慧企業能夠訓練更大、更複雜的模型。

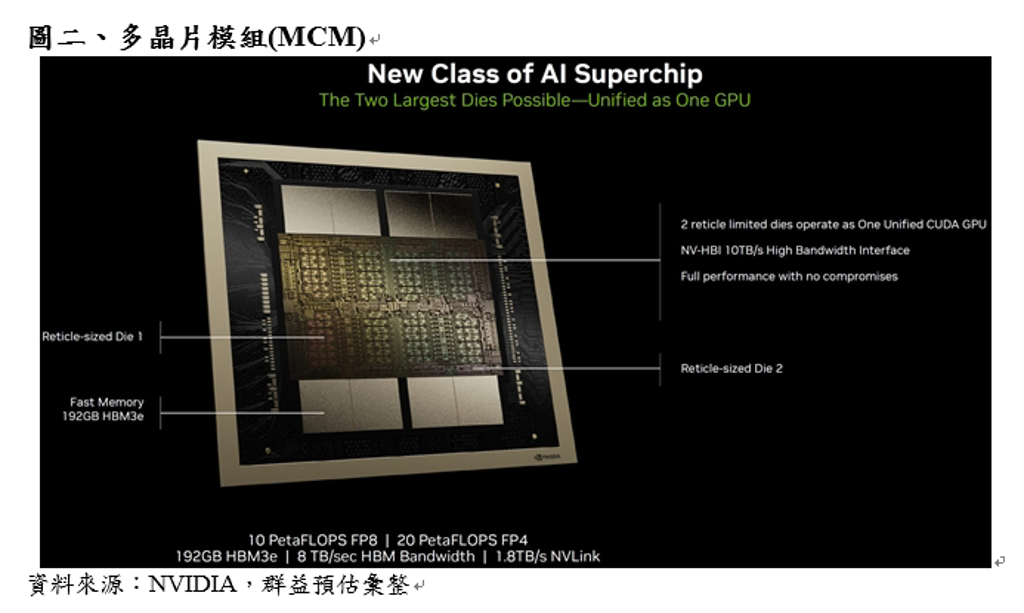

GB200用多晶片模組(MCM):

新的小晶片設計,即多晶片模組(MCM),是 NVIDIA 的一項重大創新,標誌著封裝技術的重大轉變。這種設計使得GPU能夠靈活適應不同的客戶需求,而無需大幅改變CUDA核心的數量。預計這將顯著改變 GPU 叢集的架構,以支援新的 MCM 方法。與先前使用單一大晶片的單晶片設計不同,小晶片技術可以提高生產效率,並有可能提高製造過程中的產量。台積電的 CoWoS(基板上晶圓晶片)技術在實現這些新封裝技術方面發揮關鍵作用。NVIDIA GB200 Grace Blackwell超級晶片架構透過900GB/s 超低能耗 NVLink 晶片間互連將兩個 NVIDIA B200 Tensor Core GPU 連接到 NVIDIA Grace CPU。為獲得最高的AI 能,GB200 驅動的系統可以連接到今天也宣布的 NVIDIA Quantum-X800 InfiniBand 和 Spectrum™-X800 乙太網路平台,提供速度高達 800Gb/s 的高階網路功能。Blackwell 架構 GPU 擁有 2080 億個晶體管,採用TSMC4NP製程製造,2顆GPU 晶片透過 10TB/秒的晶片間互連連接,形成單一統一的 GPU。

Blackwell還配備Micron(MU US)HBM3e記憶體。這項開發將為每個GPU 供高達141G容量和高達4.8TB/s的記憶體頻寬,突顯NVIDIA為滿足AI和 HPC應用中對更高記憶體容量和頻寬日益增長的需求而做出的努力。

NVIDIA B200採用台積電N4P製程和CoWoS先進封裝:

資料及運算需求拉升算力需求,高效能運算晶片廠商將開始採用台積電N3製程,隨GPU需求增加,NVIDIA也將提升GPU效率,NVIDIA繼推出採用台積電N7與N4的A100、H100後,B200則是用N4P製程。

台積電現已開發出多種CoWoS變體,包括CoWoS-R和CoWoS-L,以滿足不同的應用需求。CoWoS-R利用整合扇出(InFO)技術,並使用RDL(重新分配層)中介層來連接小晶片之間,特別適用於高頻寬記憶體(HBM)和SoC整合。它提供多達6層銅佈線,最小間距為4μm,並提供出色的訊號和電源完整性。CoWoS-L現在結合CoWoS-S和InFO技術的優點,透過使用LSI(本地矽互連)晶片的中介層來實現密集的晶片到晶片連接,就像Blackwell中的那樣。此版本從1.5倍標線中介層尺寸開始,旨在透過擴大中介層尺寸來整合更多晶片,從而為複雜功能提供更大的靈活性和更高的整合度。

B200採用台積電先進製程與Chiplet(小晶片)設計架構,解決高耗電量與散熱問題,單卡效率及電晶體密度,台積電先進製程與CoWoS先進封裝技術產能將持續受惠,採用CoWoS-L形式封裝。NVIDIA每2年會更新主要GPGPU架構,因此繼2022年的Ada Lovelace之後,2024年開始推出Blackwell,其中伺服器產品會先於GeForce顯卡問世。

台積電2023年即提前因應產能吃緊的現象,尤其針對先進封裝CoWoS產能,除移機挪出龍潭廠空間外,竹南AP6也啟用;據供應鏈透露,原本2H24動工之銅鑼廠,已規劃提早於2Q24,目標就是力拚1H27,能夠提供月產110K片/月12吋晶圓的3D Fabric量能。

AI、HPC等應用一片晶圓能產出之晶片僅為消費性產品的四分之一,生產製造難度更高、更複雜;台積電能達到穩定量產,對晶片業者來說,非常重要。此外,在H200轉向新記憶體HBM,也將面臨產能限制。H200到B100積極與雲端服務供應商(CSP)進行新平台銜接,數據中心功率密度是關鍵,多數CSP提前2~3年確保數據中心容量,必須提前規劃。除CSP業者外,較小型的語言模型開發商,因無法負擔ASIC開案費用,多數將使用NVIDIA方案,積少成多下,也將成訂單主力。

台積電高階製程競爭力優於同業:

目前全球擁有N7以下的晶代工產能僅台積電、Samsung(005930KS)和Intel(INTC US),Design house選擇性有限,為分散風險,原本就會在2家以上晶圓代工廠下單,主要目的為制衡各晶圓代工廠,並取得議價權,只是每年在各晶圓廠的比重不同或不同的產品。IC設計廠在晶圓代工廠投片時,晶圓代工廠若手中握有大量矽智財,有助於IC設計廠開發晶片流程。因此IC設計廠在選定投片量產晶圓廠除會考量良率、價格及交期之外,矽智財數量更是IC設計廠考慮的原因之一。

台積電是現在擁有N7以下高階製程的唯一純晶圓代工廠,良率又高於競爭對手,高階產能全球最多,加上台灣擁有一個完整豐沛的半導體生態系,使台積電競爭力優於同業。無晶圓廠半導體的庫存在2023年結束調整,庫存恢復到健康的水準,預期2024年對台積電會是健康成長的一年,尤其得益N3技術持續強勁成長、市場N5技術和AI相關需求。台積電預估2024年半導體產業成長率,YoY>+10%(不含記憶體部分),但Foundry YoY+20%,台積電2024年美元營收YoY+21~+26%。台積電憑技術領先及差異化,營運將優於產業平均。