Leadership in PCB Design Demands Constant Innovation

Cadence OrCAD is a driving force in the PCB design industry. In order to help designers keep up with the constant pace of change Cadence has been accelerating the pace of innovation delivering a stream of updates and product enhancements to users. The release history below provides insight into industry-first capabilities made available to customers such as real-time design, DesignTrue DFM, constraint manager, in-design analysis, and more.

New Feature Highlights:

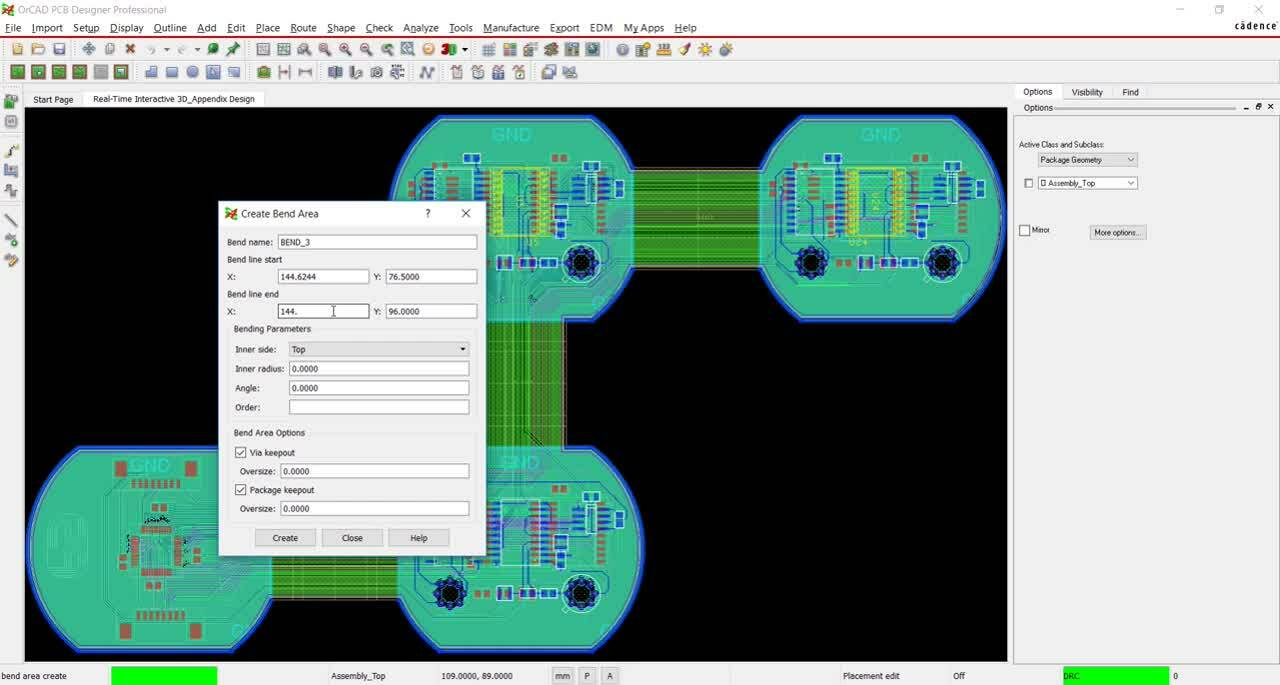

Real-Time Interactive 3D Design

See how interactive 3D in OrCAD helps you design in real time with greater accuracy.

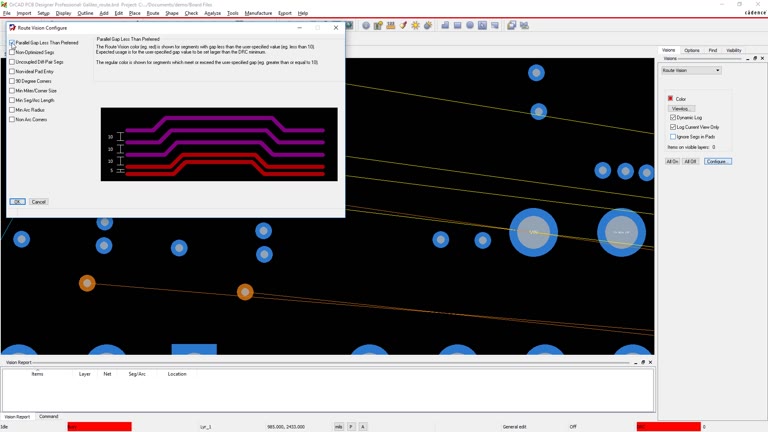

Real-Time Route Analysis

Real-time interactive checks help you easily find and fix common route quality issues that manufacturing DRC signoff checks miss.

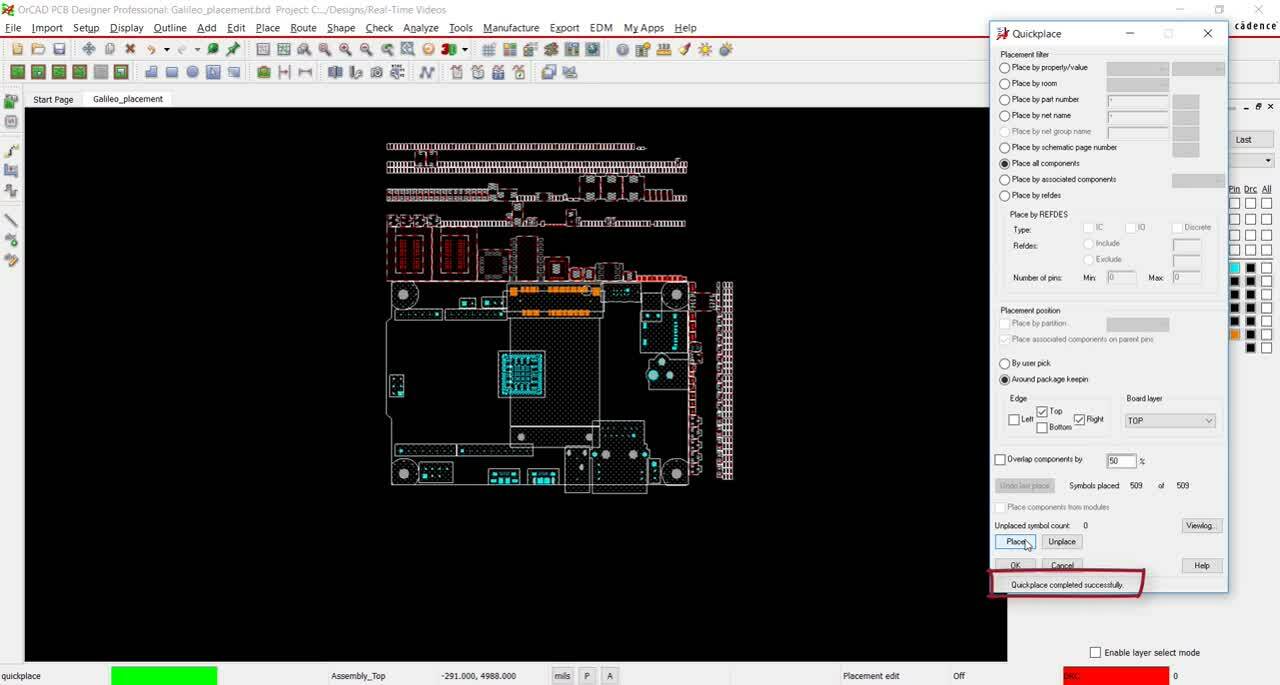

Real-Time Placement Analysis

Visual indicators of length constraints help you meet delay propagation and total etch length goals when placing components.

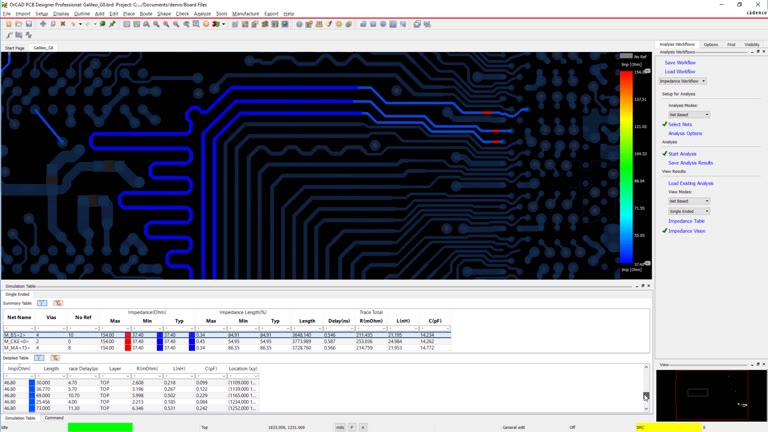

Real-Time Impedance Analysis

Easily and quickly identify impedance discontinuity issues visually, without simulation models or extensive signal integrity expertise.

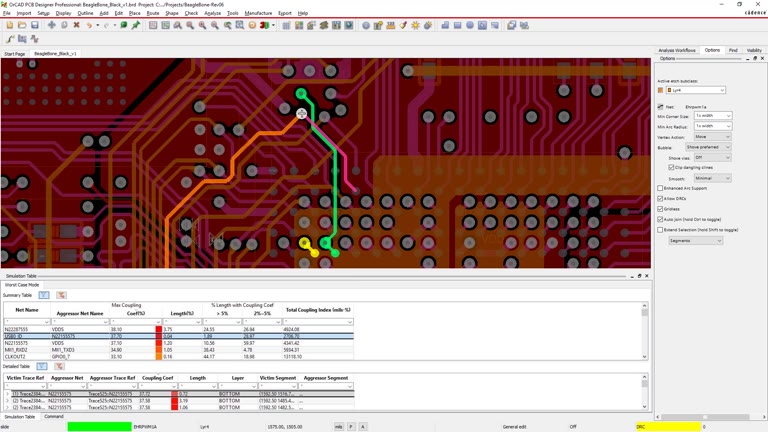

Real-Time Coupling Analysis

Easily and quickly identify coupling issues without always having to rely on the SI expert.

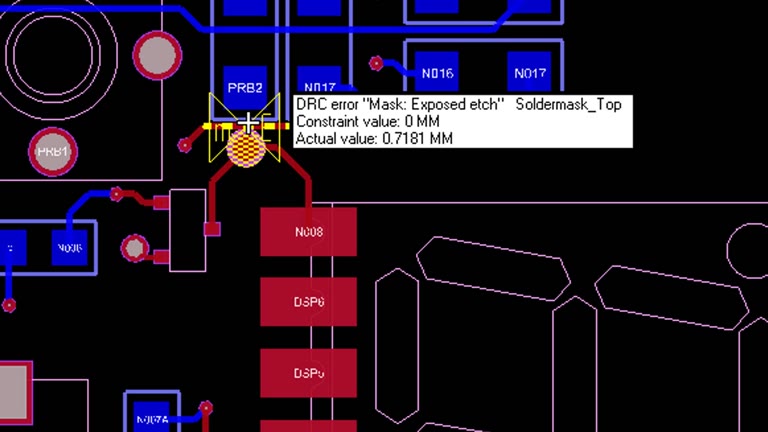

Real-Time Manufacturing Checks

Break out of the find, fix, reiterate cycle with over 200 configurable real-time design for manufacturing checks and get your design right the first time.

Full Release History:

Version Notes:

- Cadence provides bi-weekly updates to its products to fix issues and defects as quickly as possible for customers

- New functionality is also delivered through quarterly incremental releases (QIRs).

- Customers are encouraged to stay on the latest update within a release as they will not only get access to any fixes but will also have access to new features (as described below) available through the QIR stream.

Related Links

Version 23.1.1

Products Covered: OrCAD X Capture CIS | OrCAD X PCB Editor| OrCAD X Presto | PSpice

OrCAD X Capture CIS

23.1.1

ASME 2 level Revision Scheme Support. Automatic ASME 2 level alphanumeric revision scheme within cloud workspaces.

LiveBOM Cross-probe. Cross-probe between LiveBOM and the schematic to efficiently identify at-risk components in the design. OrCAD-X Pro

LiveBOM On Premise CIS Support. Connect to on premise CIS database within LiveBOM to analyze supply chain risk for CIS database components in your schematic designs. OrCAD-X Pro

LiveBOM Enhancements. Enhancements to LiveBOM and ease of use with the inclusion of supply chain lead time and customizable property columns. OrCAD-X Pro

OrCAD X PCB Editor and OrCAD X Presto

23.1.1

Design Review and Markup Improvements. Easily archive and remove embedded comments to share the design with external users and partners.

3D Enhancements. 3DX canvas has been improved in both OrCAD X PCB Editor and OrCAD X Presto to include cutting planes, material colors, transparency control for all 3D objects, 3D DRC display options, and measuring in 3D.

OrCAD X Presto

23.1.1

Object Visibility Improvements. Incorporate stipple patterns for improved object visibility. User-defined views allow you to save views and recall the visibility display in OrCAD X Presto.

Footprint Enhancements. Updates to editing footprints including mass editing of pin locations through the search panel, pad preview in search, and DXF import for footprints.

Paste Special Improvements. Preserve the location of copied shapes for easy replication.

LiveDoc Enhancements. Dimension improvements including alternate units and user-controlled text, panning and zooming improvements, ISO and ASME page sizes, and definition of export PDF location.

PSpice

23.1.1

ISO Transient Sources. ISO Transient sources for automotive applications including ISO 7637-2 for electrical disturbances form conduction and coupling and ISO 16750-2 for environmental conditions and related testing.

Performance Improvements. Parallel simulation support for parametric sweep, temperature sweep, and Monte Carlo Analysis on desktop to improve performance.

Noise Contributors. Control noise contributors in noise analysis to produce an accurate simulation.

Audio Simulation Support. Use a .wav file as a simulation input or export a .wav file as an output to perform audio simulations.

Simulation Personas. Use and create PSpice simulation personas as a simplified way to globally apply simulator options.

Version 23.1

Products Covered: OrCAD X Capture CIS | OrCAD X PCB Editor| OrCAD X Presto | PSpice

OrCAD X Release. Innovative design platform focusing on providing a cohesive and comprehensive solution for all design requirements.

OrCAD X Capture CIS

23.1

- Enhanced Help Documentation. Cadence Doc Assistant presents help content as individual easy-to-read topics and has improved the speed and relevance of search capabilities. New documentation has been provided for library and part management, part authoring, and more.OrCAD-X

- Enhanced Component Explorer. Access all the library sources along with complete part details in a unified view. The intuitive user interface provides access to various libraries supplied by Cadence, PSpice libraries and models, and external providers.

- Integration with Content Providers. A new content provider has been integrated into the unified CIS environment. In addition to Ultra Librarian and SamacSys, SnapEDA can now be accessed directly through the schematic.

- Integrated Part Authoring. Create new components from scratch using available libraries or existing parts from content providers. An easy-to-use dialog box lets you easily configure a description, category, logical symbol, footprint information, PSpice models, and electrical specifications. Incorporate lifecycle status, manufacturing part numbers, and more.

- Part Template Creation. Quickly create parts from templates containing verified symbols, footprints, models and properties and organize the parts in the workspace efficiently.

- Teams and Workspace Support. OrCAD X provides a new collaborative development environment to create shared workspaces containing work-in-progress components, projects, libraries, and design files. Create multiple workspaces for different projects and user needs. Share workspaces, define user access and roles to efficiently collaborate with team members.

- Workspace Content Management. Cloud optional workspace allows you to access data from anywhere and sync data between the local disk and cloud to keep all team members up-to-date.

- Seamless Integration to OrCAD X Presto. OrCAD X Presto is fully integrated into Capture CIS allowing you to perform design synchronizations from the schematic to PCB and vice versa. Cross-probing capabilities between the schematic and PCB help to efficiently complete the layout design.

- LiveBOM. LiveBOM is a dynamic bill of materials (BOM) that is generated using up-to-date supply chain data with zero configuration. The rich UI provides live part status from cloud libraries including real-time component availability, price data, alternative parts, life cycle status, dynamic part information and more.OrCAD-X Pro

OrCAD X PCB Editor

23.1

- Enhanced Documentation. Cadence Doc Assistant presents help content as individual easy-to-read topics and has improved the speed and relevance of search capabilities.

- Design Review and Markup. Facilitate a collaborative design review environment with the ability to markup and comment design feedback directly in the PCB canvas. Markups are stored in the design database, streamlining the design review process.

- Counterbore/Countersink. Define secondary drill definitions on either the primary or secondary side.

- Microvia Slot. Expanded the capability of microvia drill support beyond circle and square-plated holes to include microvia slot. This allows rectangular or oval-plated slots while following standard microvia constraints in the design.

- Drilled Hole Padstack Definitions. Drilled hole fields for circle and square holes as well as round slot fields for rectangle and oval shot holes have been added for accurate unit-controlled values of the drill hole size before plating and tolerances.

- Multi-Drill. Pitch values for rows and columns can now be defined to calculate the spacing automatically for a multi-drill.

- Freeze/Unfreeze Dynamic Shapes. When dynamic shapes need to remain constant to protect critically circuitry and maintain design intent, suspend or freeze dynamic voiding instead of converting to static shapes. Once frozen, new objects entering a shape will not void and will generate a DRC error.

- Zone Adherence for Symbol Pins. Components placed in a zone with some of the pins protruding into another zone can cause buried or floating pins. Easily check to verify that all pin pads of a component exist on the same placement layer.

- Nested Zone Support. Designate stackup differences in particular areas of your rigid-flex designs by defining one zone inside another for scenarios where one shape needs to be surrounded by another.

- Updated Zone Boundary Editing. Zone modifications can now be performed without activating Shape Edit Application Mode.

- Fill-In Materials. Define the fill-in material for multi-layer PCBs to account for the different dielectric constants that affect the electrical characteristics of conductors running across the dielectric.

- Updated Dimension Line Width. Define dimension parameters to apply a line width globally for all dimensions.

- Z-Copy Enhancements. Define the net during Z-copy to copy etch shapes to other layers. Incorporate a subclass wildcard to copy the shape to multiple layers.

- Place Replicate Enhancements. A new delete option will remove routing from the previous module for components that are part of another module.

- Netlist Import Enhancements. Reuse device files and component definitions that are currently in the design when loading an updated netlist.

- Net Short Report. New net short properties report is available to easily find all the objects in the design with the Net short property to verify the nets being shorted.

OrCAD X Presto

23.1

- OrCAD X Presto Release. A New layout environment offering a cutting-edge solution for PCB design. Cloud-connected and unconnected modes allow you to work based on your preferences and requirements.

- Efficient Design GUI. Intuitive, capable, efficient, and accessible GUI offering compact menus and a streamlined workflow to design quickly and efficiently. Informative and interactive panels provide insights, accelerate search and navigation, and allow efficient management of properties and visibility to design productively.

- Improved 3D Engine. An integrated 3D viewer allows seamless transition between 2D and 3D views and helps designers perform fast and accurate 3D analysis with 3D clearance design rule checks (DRCs) and enhanced visualization capabilities.

- Accelerated Real-Time Manufacturing Documentation. LiveDoc provides a templated real-time approach to creating manufacturing documentation efficiently. Easily add pre-configured views to create the required documentation and artwork for manufacturing. Changes made in the PCB design are updated in real-time on the manufacturing documentation, saving time and eliminating errors.

- Design Review and Markup. Facilitate a collaborative design review environment with the ability to markup and comment design feedback directly in the PCB canvas. Markups are stored in the design database, streamlining the design review process.

- Enhanced Help Documentation. Cadence Doc Assistant presents help content as individual easy-to-read topics and has improved the speed and relevance of search capabilities.

- Symphony. Symphony integration into OrCAD X Presto allows two designers to work concurrently on the same PCB design in real-time.

- Rigid-Flex Improvements. Rigid-flex improvements to OrCAD X Presto include real-time bending in 3D, easier management of zones and bends with streamlined access to creation, modification, rule assignment and more.

PSpice

23.1

- Enhanced Help Documentation. Cadence Doc Assistant presents help content as individual easy-to-read topics and has improved the speed and relevance of search capabilities.

- Modeling Applications for Digital Devices. Wizard-based Modeling Application support for efficient creation of digital models including gates, digital pulse, digital stimulus, flip-flops, and latches.

- Single Simulation for Modeling Temperature Variation. Include temperature coefficients in model definitions, express temperature as a function of time, and perform a single simulation to understand the effect of temperature variation.

- Enhanced Exponential Sources. Model and simulate repeated exponential electrical fast transients (EFTs), commonly required in stress testing of AC power mains, automotive DC electrical systems, ethernet and data lines.

- Enhanced Debugging for Convergence Errors. Enhanced error and warning messages for expressions leading to high or abnormal values helps users pinpoint issues and ensure convergence.

- Modeling Frequency-based Impedances. Input data points from the measured inductor response in the laboratory or extracted datasheet information to quickly and easily model non-linear and frequency dependent impedances.

Version History

Version 22.1

Products Covered: OrCAD Capture | OrCAD PCB Editor| PSpice

OrCAD Capture

22.1

- Unified Component Information System. View, search, and place components from PSpice libraries as well as SamacSys and Ultra Librarian in one centralized location with an intuitive user interface.

OrCAD PCB Editor

22.1

- On-Canvas Structure Update and Variant Creation. When reusing structures multiple times, easily update one instance and push the changes to all instances.

- Dimensioning Update. Easily make changes to a dimension without having to delete and regenerate it.

- Route Keepout Exception. Easily locate stacked vias and flag them with DRC markers in restricted areas.

- Performance Enhancements. Enhancements include better performance on designs with a large number of DRCs, faster update to smooth, better move performance, better performance for shape parameter per layer override, capping of command window messages, and faster DRC checking on designs with negative layers.

- Expanded GPU Support. GPU support now includes modern discrete or integrated GPUs from Intel and AMD. Enhancements to NVIDIA GPUs include performance gain in panning and zooming and augmented quality of display.

- Normalized Forms for High Resolution Displays. Easily specify a scaling factor to normalize forms that are partially cut off due to display scaling in devices with 4k or higher resolution.

PSpice

22.1

- Creating Frequency-Based Impedance Using Behavioral Sources. Easily model an inductor or impedance that varies with frequency using frequency tables in CSV format.

- Expression Support for Parametric Values. Support for expressions in the PSpice Modeling Application has been extended to the digital clock source, DigClock.

- Noise Analysis Output Enhancements. Define the number of top noise contributors to be reported during noise analysis.

- Enhancement of Zero Value Resistors. PSpice now supports simulation for circuits containing zero value resistors.

- Smoke Analysis Enhancements. Automatic calculation of power dissipation deration for custom-derated resistors. Hierarchical components can now be filtered in the smoke analysis results.

- 3-Sigma and 6-Sigma Monte Carlo Analysis. Automatically calculate both the 3-Sigma and -Sigma values during Monte Carlo Analysis for a greater level of accuracy.

Version 17.4

Products Covered: OrCAD Capture | OrCAD PCB Editor | PSpice

OrCAD Capture

QIR 3

- Fully Integrated PCB Viewer. Access the PCB viewer directly from OrCAD Capture and cross-probe between schematic and PCB without needing a PCB license.

- CIS BOM Variant. Support for hyphens and underscore in BOM Variant names.

- Occurrence Part Update. copy-paste occurrence-based parts across the design. Occurrence properties of selected instance are preserved and copied in the new design.

- Access to TI Libraries. Access additional Texas Instrument Libraries from OrCAD Capture including 5000 TI-PSpice Models across 100 unique model categories and as many as 4000 test circuits.

QIR 2

- Design Sync Updates. Dedicated actions for updating schematic and layout individually.

- Schematic Print Updates. Increase schematic PDF readability with the ability to set the schematic print theme independent of the canvas theme.

QIR 1

- New OrCAD Capture Start Page. After installing QIR 1, as you launch OrCAD Capture, you will see a renewed, content-rich, and reorganized Start Page. It has been designed for you to easily access a variety of information and projects. From this page, you can read about OrCAD Capture, go through brief descriptions of the available features, and access quick start guides and video walkthroughs. You can also access help content, product announcements, and industry news. The page provides contact information for your local channel partners or Cadence Customer Support.

17.4

- Simplified Project Creation and Simulation Flow. The 17.4-2019 release introduces the concept of universal projects, which allows you to create a project without having to select a project type. Further, with the new user interface, you can create a project along with the option to enable PSpice simulation.

- Streamlined Workspace. OrCAD Capture provides you with a large set of user-friendly tools and features to easily capture your schematic design. With the 17.4-2019 release, the workspace has been enhanced to ensure fast schematic design creation in an optimized manner. Many new improvements have been done in the Capture workspace to ensure greater ease of use and a satisfactory user experience.

- Application and Canvas (Schematic Page) Theme. In the 17.4-2019 release, Capture opens in a dark theme by default. A dark theme reduces power usage, improves visibility, and makes it easier for screens to be read.

- Well-Organized Toolbars. Toolbars have been reorganized according to function, and the icons in these toolbars are arranged based on their menus. You can toggle individual icons on or off in the toolbar.

- Workspace Customization. Panes are now displayed consistently across all OrCAD applications. All resources opened from a project are displayed as horizontal Tabbed Documents in the canvas area. By default, all panes displaying any kind of output are at the bottom of the application. If multiple panes are open in the output window, they are displayed as docked and tabbed panes.

- Enhanced Search Pane. The Find command is now available as a separate pane, called the Find pane. It allows you to specify a property value string and lets you select the object that you want to find. Capture then searches for all objects that match the specified string.

- Online DRC. The enhanced user interface of Design Rules Check introduces a new option—Online DRC. Set this to On if you want to check and list design rule violations dynamically as you create or update a schematic design. The Design Rules Check window enables you to set the rules to be run in Batch and/or Online mode.

- Design Sync. To efficiently and easily synchronize changes from schematic to layout, and from layout to schematic, a new user interface, Design Sync, has been introduced in 17.4-2019.Using the Design Sync window, you can view the differences between a schematic and the layout for a board, and synchronize the layout from schematic or schematic from layout. Designed with the capability for in-memory synchronization, you can use Design Sync to review the type of change, addition, modification, or removal of a design object without saving the design/layout.

- Accessing External Parts from Capture. Using the Place – Search Providers menu, you can search for and download millions of electronic components, symbols, footprints, manufacturer datasheets, and 3D STEP models from Cadence-supported content providers — SamacSys and Ultra Librarian. You can easily find the part you require and place it in your design. The part, its associated metadata, and any available ECAD models, are saved to your local library.

OrCAD PCB Editor

QIR 3

GPU Acceleration Rendering. Leverage GPU in Allegro Layout Editors to improve response time during panning and zooming, toggling layers, and render quality.

DRC Browser Updates. Navigation improvements for the DRC Browser and the ability to waive DRC by group select.

Fillet DRC Control. New analysis mode option to enable line based checks for fillets.

Shape Performance and Quality Updates. Improved shape performance for copper pours and editing smooth shapes. Fast mode replaces rough mode and drastically improves the performance during active etch editing including slide, add connect, move, and more. Improved performance in shape voiding quality including crosshatch shape fill improvement, fillet void quality improvement, and trim void improvement.

3D Canvas Updates. Isometric view has been added for the bottom side of the board. Other updates include realistic plating thickness, increased model realism, and secondary model support.

Reuse Module Enhancement. Dynamic shapes are automatically converted to static shapes to ensure consistent voiding. Modules applied to the design remain locked to avoid accidental modification. Addition of copper planes, constraint regions and text notes within the module file. Quickly swap a placed reuse module with a different variant in one or multiple locations.

Scribble Enhancements. Multi-pin scribble support when routing allows you to digitize a path through a pin field to make connections. Recognizes the same net pins and snaps to center while routing.

QIR 2

Viewer Integration. Launch PCB Editor viewer from the project hierarchy.

3D Canvas enhancements. 3D mapper now a part of 3D canvas, replacing Allegro (2D) menu. Simplified use model and GUI enhancements. Improved accuracy of collision detection and distance measurements. Additional support for mapping native CAD models (Parasolid, Siemens NX, CREO, SOLIDWORKS).

IPC2581 enhancements. Additional support for rigid flex (bend detail and stack-up profiles), Countersink/counterbore, square drill features, net shorts, and impedance specifications and nets.

IDX enhancements. Bend sequence ordering, Geometry use identification, primary pin identification, and time stamps.

QIR 1

PCB Panelization. Setup and manage your fabrication panels directly within PCB Editor (OrCAD Pro & Allegro Feature).

New Design Setup Workflow. You can now use the new Design Setup Workflow to prepare for analysis by setting up your design for the different checks. You can set up cross-section, DC nets, components, Xnets, and differential pairs. You can then save the design with the changes. As with all other work flows, you can access this workflow from the Analysis Workflows pane (Analyze – Workflow Manager).

3D Canvas Updates. A number of improvements and enhancements have been made to the 3D canvas including:

- Performance Improvements. In this release, performance improvements is a top priority resulting in greatly improved launch times and reduced memory usage.

- 3D Canvas Filter Dialog. You will see the re-designed filter dialog. With this redesigned dialog. You have the choice of selecting what layers to visualize in 3D Canvas – All Layers or Outer Layers only, and what objects you wish to bring into the 3D Canvas. You can now visualize much larger designs in 3D Canvas by eliminating memory straining objects.

- Nets Pane. A new pane has been added to 3D Canvas – the Nets pane. Prior to this release, nets were visualized on the 3D Canvas, but no underlying information regarding nets were imported. With this release, net information (names, type, properties, and so on) are also imported into 3D Canvas and the new Nets pane allows you to control how to visualize the nets in 3D Canvas. You can select All Nets (the default view) and any other groups of nets contained in a design.

- Variable Highlighting. Prior to this release, components selected on the 2D side or selected in 3D Canvas were shown in 3D Canvas as selected (red). With this release, two new highlighting choices are available – Dim and Vanish. With the Dim option, selected objects still appear on the canvas as red while the remainder of the elements are dimmed. With the Vanish option, selected objects appear on the canvas as red while the remainder of the elements disappear.

17.4 Base Release

IPC 2581 Spec Properties. By defining a SPEC that is composed of the fabrication notes, the notes become part of the IPC-2581 data and are directly read by an IPC-2581 viewing tool, reducing the need to locate the correct drawing or document to read the notes. Another example would be to define assembly notes for a heat sink to be added to a part. The assembly note might instruct users to add a specific thermal epoxy first, then add the heatsink after the epoxy is applied.

Mask Defined Pin Annular Ring Check. A new Mask Defined Pad check has been added to the Design for Manufacturing Annular Ring checks and the DesignTrue DFM Wizard template file. There are two common types of padstack definitions when it comes to soldermask to pin pad size ratios. The first, metal-defined padstack (sometimes referred to as non-mask defined padstack), is where the solder mask opening is typically larger than the pin pad. The other is a mask-defined padstack, where the solder mask size is typically smaller than the pin pad. The mask-defined pad is often used for BGA components to contain the solder ball within the pin pad and prevent outflow of solder.

Hierarchical Route and Via Keepouts. You can now define keepout by layer type and location using the additional Route and Via Keepout subclasses that have been added to Symbol Editor. Following a model similar to Constraint Regions, use the OUTER_LAYERS, INNER_SIGNAL_LAYERS, and INNER_PLANE_LAYERS subclasses to create keepout shapes.

Contour Routing Update. The 17.4-2019 release now supports the previous Enhanced Contour behavior as the default contouring method. In addition to the previously supported functionality of latching/unlatching and shoving, this release focuses on ease of use and power by adding additional spacing controls and full constraint region support.

Copy/Paste Update. In previous versions of layout editors, copying of objects was performed by selecting objects and pasting them to one location at a time. While the use model was simple, the functionality was limited. The 17.4-2019 release aligns the copying functionality of the layout editors with other popular software applications by adding familiar behaviors. This new copy command combines the precision of single click or single location pasting with the power of window select or multi-location pasting. As with most applications, copied objects are buffered for pasting at a later time. You can paste the last copied object at any time simply by using the paste command.

Copy. The Copy command now adds the selected objects to a buffer and automatically starts the Paste command to enable the placing of objects on the canvas.

Paste. The Paste command supports all legacy “copy” options as well as new support for shape net retention. In addition to these options, pasting can be used in two different manners:

- Single Location Pasting

- Copying of objects and pasting at one location per click

- Object snaps to the singular selected object or location

- Multiple Location Pasting

- Copying of objects and pasting at multiple locations through window select

- Objects snap to all selected objects

- Single Location Pasting

3DMechanical Symbol Transparency. Designers who wish to “peek” inside a PCB assembly encased with a mechanical cover can now do so. Now look through the mechanical cover into an assembly by setting the global transparency/opaqueness setting.

Unplated Holes in Footprints. Unplated holes in footprint (.dra) files can now be visualized when the footprint is brought into 3D Canvas. Previously, unplated holes were not represented.

STEP Models and Pastemask. In some system designs, such as complicated telephony devices, even the most minuscule space is critical. With the 17.4-2019 release, the position of 3D models can now be globally adjusted to take the thickness of solderpaste into account in the “z” direction. By default, the STEP model location in the “z” direction is the bottom of the model located directly on top of the copper pads.

PSPice

QIR 3

Access to TI Libraries. Access additional Texas Instrument Libraries from OrCAD Capture including 5000 TI-PSpice Models across 100 unique model categories and as many as 4000 test circuits.

Improved Usability. Auto launch of PSpice on new project creation, updated menus, and updated PSpice search.

MATLAB 2020/2021 Support. MATLAB 2020/2021 support is now available for PSpice co-simulation flows.

QIR 2

Usability updates. Get notified for missing parts for your PSpice models as you place them with Online DRC. Navigate warnings and errors with cross-probe between DRC and schematic. PSpice parts are loaded automatically when a new PSpice project is created. Improved capture integration with the ability to view PSpice models within Capture.

New modelling applications. Easy-to-use DIODE and MOSFET model parameters from device datasheet, specifically targeted for power applications.

Version 17.2

Products Covered: OrCAD Capture | OrCAD PCB Editor| PSpice

OrCAD Capture

QIR 7

Enhancements in Part Editor. With QIR 7, you will see the following enhancements in part editor:

- In-place editing of text objects

- Enhanced Edit pins dialog box

- View package information

- Additional grid control

- Integration of Constraint Manager with OrCAD Capture. Constraint Manager is a cross-platform, spreadsheet-based application used to manage constraints across all tools in the Cadence® PCB and IC Package design flow. With this hotfix, Constraint Manager is integrated with OrCAD® Capture.

QIR 5

Simplified Interface for Associating a PSpice Model. You can now accomplish the following tasks to associate a PSpice model using a simplified user interface:

- Select a PSpice model library

- Display and select the matching models

- View model text and symbol graphics

- Perform pin-port mapping

- Launching Footprint Viewer from Capture. In this release, Capture enables you to view the footprint associated with a part. The footprint viewer provides a two-dimensional view of the footprint symbol of the part selected on the schematic. Along with the footprint symbol, the viewer also shows the pin numbers and pin names.

- New and Simplified Part Editor. You will see a new version of the part editor. A new user interface has been introduced where you can view and modify all properties in a single integrated pane, called Property Sheet.

QIR 4

Performance Improvement. Performance has been improved for various design specific cases, such as designs with large number of netgroups.

QIR 1

Design View in HTML. This new feature allows you to export a complete schematic design as a single HTML file, and view the design in the specified internet browser (Google Chrome recommended).

Saving Design Differences to HTML or Excel. OrCAD® Capture Design Differences Viewer now supports the ability to save the design differences into HTML files (.html) or Excel files (.xls).

Passport Protection to a Design in Capture. You can now add a password to a design, remove an existing password applied to a design, or modify an existing password applied to a design.

Configuring Properties. You can configure the Find window properties and Browse Parts window properties using the Configure Properties window.

New Utilities. New utilities have been added in OrCAD Capture to automate some of the manual tasks, including: Communication Server, Replace Path in Design Cache, Show All Open Libraries and Design, Customize Page, Check/Correct Corrupt Library, and Find and Replace Text.

Display Checkbox in Add New Property Dialog. Enable display of user-defined properties so that you can set display properties while creating a new user-defined property.

Updated Property Editor Filter in the Properties Editor Window. Updated and flow-wise property spreadsheet filters are now available, so you don’t need to search for commonly used properties for a flow.

Global DRC Settings for Global Environments. A new option, Use Global DRC Settings, has been added in the DRC tab of the Extended Preferences Setup window. By enabling this option, you can use the same DRC settings globally for various different designs to enable standardization of a DRC setting across projects, sites, and teams

17.2 Base Release

Design Difference Viewer. New feature to perform logical and graphical comparisons between two designs, two schematic folders or two schematic pages and view the difference report in the form of a portable HTML format. (Watch Demo Video)

Open Demo Design. The new Open Demo Design browser gives access to more than 150 demo designs made available from different locations, collated together to help users better understand Capture, Capture CIS and Capture _ PSpice Flow.

Export – Import XML. OrCAD Capture provides you the capability to convert Capture designs to XML format and vise-versa based on the requirement.

ISCF Export. Introducing direct ISCF (Intel Schematic Connectivity Format) feature for automating Intel-based design reviews to export hierarchical schematic designs in an Intel-approved format helping you optimize the design review process.

PDF Export. The new PDF export functionality lets you export Capture design as PDF file and provides intelligent design information.

Extended Preferences setup. The extended Preferences Setup window allows you to modify additional application settings in OrCAD Capture like Command Shell, design and libraries, design rule check, CIS, NetGroup, NetList, and Schematic.

Advanced Annotation. The new advanced annotation feature lets you annotate multiple schematic pages at a time giving them complete control over their component annotation process in the design cycle. (Watch Demo Video)

OrCAD PCB Editor

QIR 7

Design for Fabrication Rule Enhancements. In the Design for Fabrication constraints, a new category Copper Features has been added in this release. This category applies rule to cover minimum line width, antenna, and acid traps.

Design for Assembly Rule Enhancements. A new category PkgToPkg Spacing has been added in the Design for Assembly constraints. You can now maintain the DFA table within Constraint Manager and assign different DFA rules based on stack up technology, specifically within rigid-flex designs. All existing functionalities are still maintained from previous versions.

Design for Testability Rule Enhancements. A new Design for Test constraints have been added in the Manufacturing category in the QIR 7 release. These group of checks are related to issues in the final testing of the PCB assembly.

DesignTrue DFM Ecosystem. To make designs ready for fabrication, the information about various manufacturing constraints and rules and the supported values are obtained from PCB fabricators in the form of spreadsheets. The spreadsheet is then transferred into Constraint Manager by a PCB designer. This process is error-prone and time consuming. The easiest way to obtain the rules would be in the form of direct import of fabricator rules into the Constraint Manager using technology files recognized by Constraint Manager.

DesignTrue DFM Web-Based Rules Request. The DesignTrue DFM Partner Program was developed to facilitate the request for fabrication rules directly from the supplier and receive those rules in the constraint technology file format. You can then directly import the rule files received into Constraint Manager.

To request rules, open the request login site from a Web browser at https:\\pcb.cadence.com\dfm_customer.

3D Canvas Update. The recently productized 3D Canvas continues its growth and maturity with the QIR7 release. With additional features still under development, this release covers incremental updates that will enhance the user experience.

Selecting a specific area of a design to visualize in 3D is now easier with “window select” on the 2D workspace

The popular Cutting Plane feature has been supplemented with a “reverse cutting plane” option

The original Perspective View has been paired with an additional Orthographic View choice

The 3D Canvas now recognizes STEP model colors assigned in the STEP Package Mapper

Color Theme layers now have transparency control sliders and objects falling within holes

Cutouts and outside the board outline are now eliminated from view

Place Vision. Place Vision, available in PCB Editor, is a graphical environment designed to increase productivity and efficiency with various component placement strategies. While the concept is similar to Timing Vision, Place Vision offers guidance with respect to:

Xnet rat filtering

Timing driven Placement

Component Association

Sigrity Technology Driven High-Speed Signal Analysis and Checking. OrCAD® Integrated Analysis and Checking is a new, unique environment blending the best of OrCAD® and Sigrity™ technologies that provides analysis and checking capability entirely within the PCB Editor framework. For rule checking, DRC and ERC capabilities continue to depend on Constraint Manager as the single cockpit. This release introduces two new workflow analysis capabilities for impedance and coupling. The workflows provide guided access to Sigrity analysis with results returned as dockable tables and plots, or as new Vision overlays.

Timing Path support for Z-Axis Delay. The Z dimension of Vias and Through Hole Pins can now be included in timing path DRC calculations.

Pin Delay Property for Extended Timing Path into Packages.