三八译码器74HC138的 使能端 的工作原理是什么?为什么设计三个使能端?

3 个回答

写在前面:答主这学期开始学数电课,刚好昨天上课讲了译码器的内容,经过今天的思考,我想到了一个我认为还通俗易懂的过程。由于不会用电脑画图,下面答案中的图片都是我手画的,可能会有些难以辨识,还望大家谅解。答主也是小白一枚,哪里说的不好还请各位大佬批评指教。

注:为了表示出来每张图之间的变化,我将后面图新增的部分用红色表示。

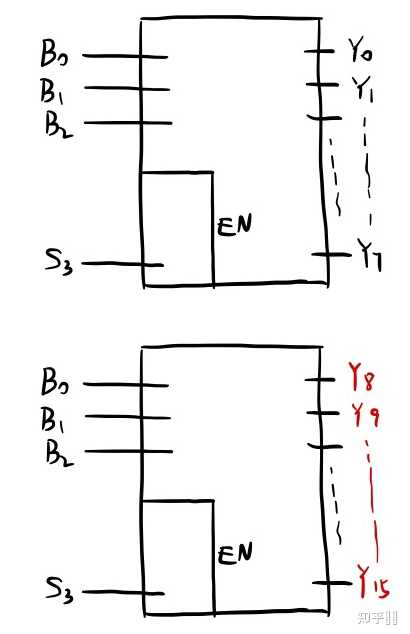

三八译码器,先想最简单的情况。输入一个三位的二进制数 B_3B_2B_1 ,一共对应输出8种十进制数0~7,也就是大概长成下面的这个样子。

现在为了控制这个门电路的开关,我们还需要加一个使能区,对这个门电路的有效输出进行控制。(为了让最后的图看起来和真实情况一样,我这里就先命名这个控制端为 S_3 了)

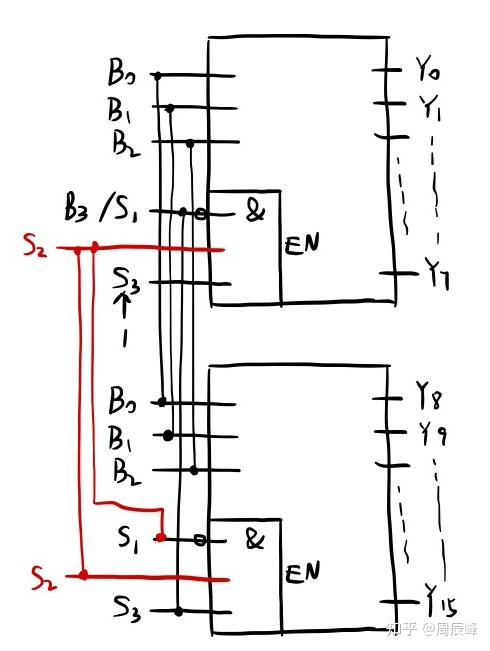

这时候看起来好像已经可以实现最基本的三八译码器的功能了,在此基础上我们还加上了一个控制开关,貌似已经可以了。但是!考虑到以后我们可能会使用两个3-8译码器进行扩展,组装成一个4-16译码器,我们目前的设计好像并不能完成这个任务。

先进行一下分析:4位二进制数代表着16中选择,扩展后我们将可以表示十进制的0~15。而对于十进制8~15的二进制数的最高位都是1,十进制0~7的二进制数的最高位都是0。那么,思路就来了:

- 后三位二进制数同时输入到两个译码器中:两个译码器中的 B_0,B_1,B_2 分别相连。

- 输入的最高位 B_3 用于选择上片0~7输出还是下片8~15输出:为了实现这个功能,我们需要在使能区再加一个控制引脚 S_1 。由于 S_3 和 S_1 共同控制使能区,所以使能区是一个与门。

- 在上片中 S_1 同时作为二进制最高位 B_3 的输入引脚:当 B_3=1 时,应选择下片输出8~15;当 B_3=0 时,应该选择上片输出0~7,故 S_1 引脚应先取非,再输入进译码器。为了让上片的S_1 能够控制上下两片译码器,将上片的 S_1 与下片的 S_3 连在一起。

- 为了能让上片的 S_1 能够独立控制上片译码器的输出,我们可以将上片的 S_3 接入高电平,这样在使能区的与门中 S_3 相当于不起作用,上片的输入完全由 S_1 来控制。

这个时候细心的知友应该看到了一点端倪:下片的 S_1 现在是一个悬空状态。而且,如果将这两个3-8译码器封装成一个4-16译码器的话,最终的形态应该是下面这样的,除了输入输出,应该还有一个总的控制引脚。

目前上片的引脚已经全被用了,要想解决上面的两个问题,似乎我们只能勉为其难再加入一个控制引脚 S_2 来担此重任了,并且上下两片译码器的 S_2 相连,上片的 S_2 还需要照顾一下下片单身的小兄弟 S_1 ,总不能让人家孤苦伶仃一个人悬在那里吧(手动滑稽)。

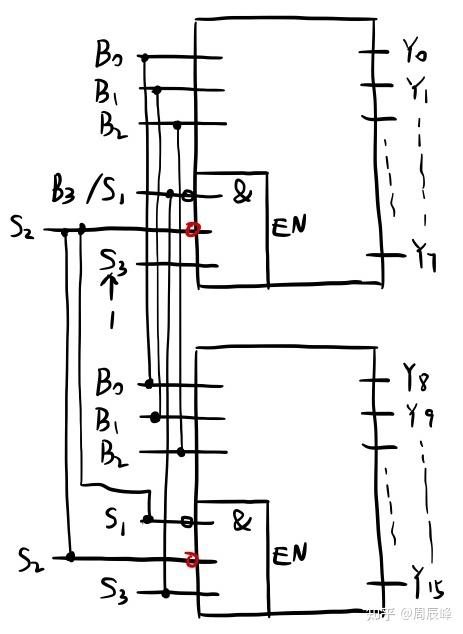

离成功只剩一小步了,我们还需要分析一下 S_2 应该是怎样的一个输入逻辑:已知总的输出有效的时候下片的 S_1 需要为0。由于下片的 S_1 的来源是 S_2 ,两个引脚同状态,故得出结论:当 S_2=0 时元件被使能,。此时为了在使能区的与门内输入逻辑1,我们需要将 S_2 的输入取反。

现在,由两个3-8译码器扩展而成的4-16线译码器就完成了。将最后设计出来的单个3-8提取出来就是下图的样子了。

写在最后:这个是答主第一次回答这类问题,原本以为语言已经组织清楚了,但是当真正开始写回答的时候还是会纠结有些地方该如何表述。虽然看问题日志这个问题已经提出来有一段时间了,不知道题主是否还需要这个回答,但是我还是打算把这篇回答写出来,也当做是对自己的一种锻炼了,让我对译码器的理解更深一点。

有哪里写的不好还望知乎大佬们批评指正!我会学习改正的!

灵活的片选吧,比如有两个138,第一个138的e3和第二个138的e1连接到同一根控制线上,第一个138的e2,e1都接低,第二个138的e3接高、e2接低,控制线高低分别选中一个138,高时选中第一个138低时选中第二个138。