ADVERTISEMENT

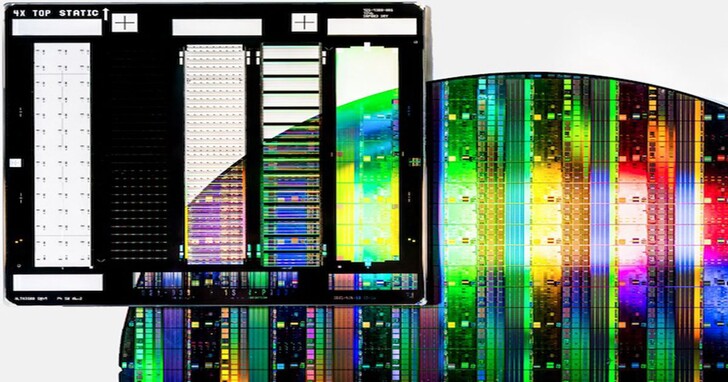

為了順利用上極紫外光刻(EUV)技術來生產晶片,半導體行業耗費了十多年時間才走到今天這一步。不過從ASML最近更新的 2024-2025路線圖來看,抵達具有高數值孔徑的下一階段,所需時間將要比預估的少得多。據悉,當前市面上最先進的晶片,已經使用了 5 / 4 nm 的製造製程。

借助 ASML Twinscan NXE:3400C 或類似的系統,結合具有 0.33 數值孔徑(NA)的光學旗艦,機器能夠提供 13 nm 的精度。對於單模方法的 7 / 6 nm(間距 36~38 nm)和 5nm(間距 30~32 nm)的製程節點來說,這樣的精度已經足夠。對隨著半導體行業向 5 nm 以下(間距 < 30 nm)轉進,業界預期先進製程 2025 年後進入埃米(angstorm)時代,High-NA 曝光技術將是關鍵。

而在後 3nm 節點,ASML 及其合作夥伴正在開發一套全新的 EVU 工具──它就是具有 0.55 高 NA 鏡頭、能夠實現 8 nm 精度,有望消除在更先進製程節點上使用多重曝光的 Twinscan EXE:5000 系列。

新款高 NA 掃瞄儀仍在開發之中,預計其結構將異常複雜、龐大、且昂貴──每台成本將超過 4 億美元。除了新的光學器件,高數值孔徑還需要用到新的光源、甚至需要新建晶圓工廠大樓以容納更大的機器──這些無疑都要追加大量的投資。即便如此,在權衡半導體器件的性能、功率、面積和成本(PPAc)之後,領先的邏輯晶片和儲存設備製造商還是更願意接納新技術,這意味著高 NA EVU 掃瞄儀對後 3 nm 時代至關重要,且各廠商對高 NA 工具的需求也將異常旺盛。

幾週前,ASML 透露其高數值孔徑 Twinscan EXE:5200 系統(EUV 0.55 NA)在2022年Q1收到了來自邏輯和 DRAM 客戶的多份訂單。此外路透社上週報導稱,該公司在五月份澄清將於 2024 年交付試點用的高 NA 掃瞄儀訂單,並將從 2025 年開始交付具有更高生產力的後續型號(超 5 份訂單)。有趣的是,早在2020至2021年,ASML 就表示已收到來自三大客戶的 High-NA 購買意向(無疑是英特爾、三星、台積電),且總計達到了 12 套。至於 ASML 已開始著手打造的首套 High-NA 系統,其將於2023年完工,以供 Imec 和 ASML 客戶開展相關研發工作。

ASML 首席執行長 Peter Wennink 表示:「我們正在高 NA EUV 方面取得良好的進展,目前已開始在位於 Veldhoven 的新無塵室中內建首套高 NA 系統。」ASML 在今年Q1收到了多個 EXE:5200 系統訂單,且 4 月份收到了額外的 EXE:5200 系統訂單。透過這些預定,ASML 收到了來自三家邏輯晶片和兩家儲存製造商客戶的高 NA 系統訂單。作為 ASML 的下一代高 NA 系統,EXE:5200 將大力推動下一代的曝光性能和生產力的提升。

據悉,ASML 的 Twinscan EXE:5200 系統較常規的 Twinscan NXE:3400C 機器要複雜得多,因而原廠的工具構建工作也需要耗費更長的時間。該公司希望在未來中期能夠交付多達 20 台 High-NA 系統,這可能意味著其客戶將不得不奮力爭搶這些機器的優先使用權。

Wennink 補充道:「我們還在與供應鏈合作夥伴展開討論,以確保在中期達成約 20 套 EUV 0.55 NA 系統的產能」。

截至目前,唯一確認使用 ASML 的 High-NA 工具的,還只有英特爾的 18A 製程節點。後者曾透露在 2025 年轉入量產,大致可以趕上 ASML 開始交付其生產的 High-NA EUV 系統的時間。不過近日,英特爾又將 18A 的上手時間延後到了 2024 下半年,並表示可借助 ASML 的 Twinscan NXE:3600D 或 NXE:3800E 系統實現 18A 製造(很有可能是利用多重曝光來實現)。顯然,英特爾希望加速推進其 18A 製程節點的推出,以從台積電手中奪回製程技術的領先地位。

然而對於商用晶片來說,多重曝光也意味著更長的產品週期、更低的產率、更高的風險、以及潛在的更低產能(即使仍有提升的空間)。最後,包括三星、SK 海力士和美光等業內領先的半導體製造商,也將不可避免地採用 High-NA EUV 來量產晶片,問題是它們尚未所說確切的時間表。

請注意!留言要自負法律責任,相關案例層出不窮,請慎重發文!