【為什麼我們要挑選這篇文章】隨著先進製程發展,晶片尺寸已進逼 1 奈米的物理極限。過去,封裝相對不受市場重視;然而在近年,「先進封裝」已成為摩爾定律的救世主。外界預期,先進封裝市場將在 2019 – 2025 年以 6.6% 的復合年成長率成長,到 2025 年將達到 420 億美元的規模。

什麼是先進封裝?為什麼它是延續摩爾定律的關鍵?(責任編輯:郭家宏)

封裝技術從未如此重要過。在今年,先進封裝技術已成為了各大晶圓廠、封測廠商甚至一些 Fabless 的重點投入領域。

9 月,聯電與封測廠商頎邦相互交換股權;在 8 月的 Hot Chips 產業熱點大會上,台積電副總經理余振華公佈了 CoWoS(Chipon Wafer on Substrate)封裝技術的路線圖,以及先進熱處理和 COUPE 異構整合技術;7 月,英特爾公佈了未來製程工藝和封裝技術路線圖,將繼續推動 Foveros 3D 堆疊封裝技術與 EMIB(嵌入式多管芯互連橋)封裝技術的應用;封測龍頭日月光則在 6 月宣佈將投入 20 億美元用於提高其晶圓封裝業務。

維持摩爾定律的關鍵:封裝技術

半導體產業鏈上下游廠商已把封裝技術提到更加重要的位置,其原因就是先進封裝實際上已成為超越摩爾定律的關鍵賽道。摩爾定律,戈登.摩爾根據自己的經驗在半導體領域做的一個預言:「在最小成本的前提下,積體電路所含有的元件數量大約每年便能增加一倍。」(The complexity for minimum component costs has increased at a rate of roughly a factor of two per year.)

摩爾定律作為半導體迅猛發展的重要推動力,從誕生開始就遭到人們的質疑——是不是再過多少年摩爾定律就要失效了?為此有人還打趣道:「預測摩爾定律要死掉的人數,每兩年翻一倍。」

如今,距摩爾定律的提出已過去了 56 年,要想在拇指大小的晶片上做出更多的電晶體與更小的製程,變得越來越困難。維持摩爾定律變得越來越困難的原因,在於人類遇到了兩個難題:一個是成本問題,全球有足夠實力嘗試 7 nm 及以下製程的晶片製造商也只有台積電、三星、英特爾三家,因為僅僅製造一座先進製程的晶圓廠就需數百億美元,這還不算日後營運維護和技術研發。

第二個則是技術上的難題,隨著晶片尺寸的微縮,短通道效應導致的漏電、發熱和功耗嚴重問題一直困擾著晶片製程的繼續微縮。當材料逼近 1 nm 的物理極限時,量子穿隧效應導致有一定的電子可以跨過勢壘,從而漏電,這個問題對於人類來說暫時是無解的,因為物理理論還沒有搞清楚這個現象。霍金從物理角度上對其做過一個總結,光的有限速度和材料的原子特性。

雖然摩爾定律到現在仍在艱難維持,但產業界也確實意識到了製程不會無限縮小下去,電晶體也不可能無限增加下去。可要知道的是,摩爾定律首先是一條經濟上的定律,然後才是工程科學方面的定律。因為降低特徵尺寸能降低晶片製造的整體成本,所以業界才會不斷追逐摩爾定律,其背後的邏輯是:半導體產業需要以一個合適的速度成長來降低成本提高利潤。

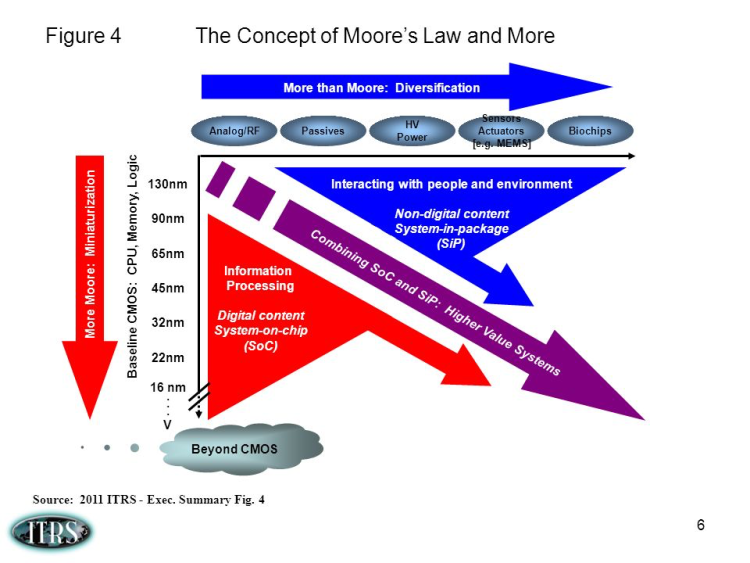

這個時候 More than Moore(MTM,超越摩爾定律)——摩爾定律之上的成長動能也因此被廣泛提出,產業界試圖從更多的途徑來維護摩爾定律的發展趨勢,而先進封裝技術已成為超越摩爾定律的關鍵賽道。

中國封測技術專家於大全曾表示,無論是延續摩爾定律,還是超越摩爾定律,都離不開先進封裝技術,「先進封裝將是撬動半導體產業繼續向前的重要槓桿。」先進封裝到底是什麼呢?為何它能作為為摩爾定律續命的關鍵技術出現?

相較於先進製程,先進封裝技術的難度較低

封裝(Package),是把整合電路裝配為晶片最終產品的過程,簡單地說,就是把製造廠生產出來的積體電路裸片(Die)放在一塊起到承載作用的基板上,把管腳引出來,然後固定包裝成為一個整體。它主要要三個作用:通過特殊材料保護脆弱的晶片、將晶片電子功能部分與外界互連以及物理尺度兼容。

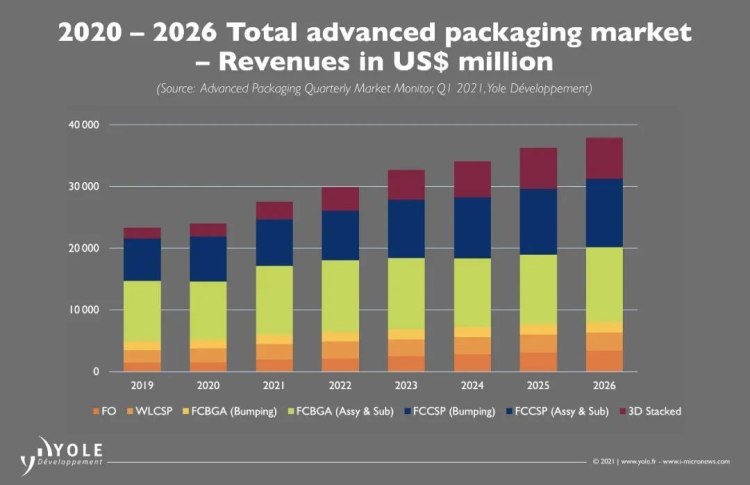

近年來,先進封裝市場也確實在迅速發展。據知名分析機構 Yole Developpement 的預測,先進封裝市場預計將在 2019 – 2025 年間以 6.6% 的復合年增長率增長,到 2025 年將達到 420 億美元,遠高於對傳統封裝市場的預期。

先進封裝其實是相對傳統封裝而言的。在業界,先進封裝技術與傳統封裝技術通常以是否焊線來區分。傳統的封裝技術通常指先將晶圓切割成單個晶片,再進行封裝的工藝形式,其包括雙排直立式封裝 DIP 與球格陣列封裝 BGA,需要銲接線路。先進封裝則包括倒裝(FlipChip)、凸塊(Bumping)、晶圓級封裝(Waferlevelpackage)、2.5D 封裝(interposer,RDL 等)、3D 封裝(TSV)等封裝技術,其技術並不需要用到線路銲接的方式。

拋開這些複雜的封裝術語,產業界將先進封裝技術提升到與製程微縮同等重要的原因,在於它能進一步提高晶片的整合度並且降低晶片製造的成本,並且,與繼續追逐先進製程不同,它暫時還不涉及到去突破量子隧穿效應等物理極限問題,沒有了這些難啃的硬骨頭,先進封裝技術看起來有良好的發展前景。

透過 chiplet 技術,先進封裝能提升晶片良率

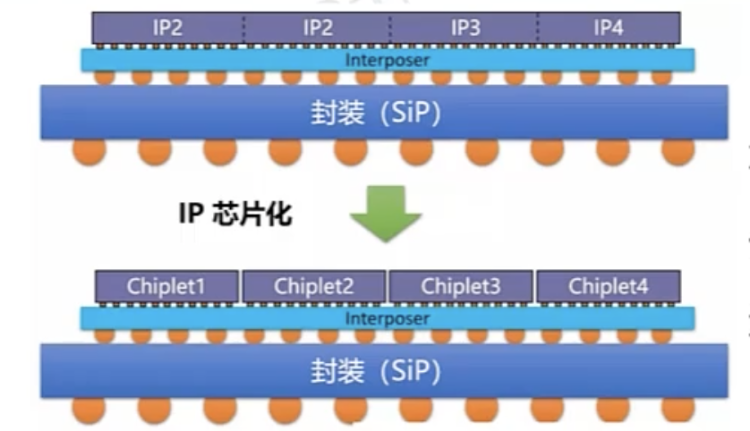

那麼先進封裝具體是透過怎樣的技術原理來實現超越摩爾的呢?這就不得不 chiplet 技術的發明,chiplet 也被稱為小晶片,它是系統級晶片(SoC)中 IP 模組的晶片化,透過 chiplet 技術可以提高良率和降低成本,同時提高設計的靈活度,縮短設計週期。

簡單來說,可以把 chiplet 技術想像成為一塊樂高積木,多個 chiplet 模組可以拼接成一個系統級晶片(SoC),而在過去,一個系統級晶片(SoC)是不能再次切割的。這樣做的好處在於,一塊完整的晶圓可以被分成更多的 chiplet,這意味著同樣良率情況下更低的成本消耗,例如在一片晶圓切割封裝時出現了一個點的損傷部位,直接做成一個系統級晶片(SoC)能切成 10 塊,假如做成 chiplet 是 100 塊,那麼這塊晶圓做成系統級晶片(SoC)的良品率為 90%,而做成 chiplet 的良品率可以達到 99%。

chiplet 技術也為異質異構的晶片製造提供了可能,這種模組化的小晶片可以實現不同架構、不同材質、不同工藝節點甚至不同代工廠生產的產品整合到一塊晶片上,由此快速產生出一個適應不同功能需求的超級晶片。

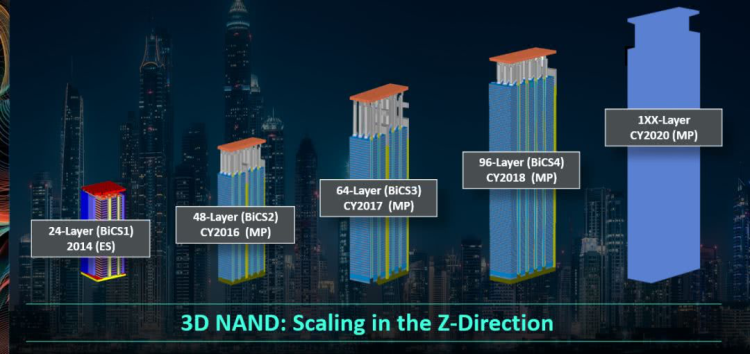

除了 chiplet 技術以外,3D 晶圓級封裝也是近年來產業界先進封裝技術的發展方向。3D 晶圓級封裝是指在不改變封裝體尺寸的前提下,在同一個封裝體內於垂直方向疊放兩個以上晶片的封裝技術,相較於傳統的 2D 電路的平面整合方式,它的整合度要更高,同等空間內可以整合更多晶片。當 3D 晶圓級封裝與 chiplet 技術相結合,還可以實現不同 IP 之間的 3D 堆疊,從而大大降低了封裝成本以及能耗。

如今,台積電、英特爾、AMD、日月光等主要晶片設計、製造、封裝廠商都逐漸在其產品中應用到了上述先進封裝技術,中國封裝龍頭長電科技也在今年 7 月推出了 XDFOI 高密度扇出型封裝技術,先進封裝所扮演的角色無疑是愈加重要了。

對中國的晶片企業而言,先進封裝或許是現下適合長期投入的優質賽道,畢竟短期內中國企業還無法透過自研或是進口來獲取 EUV 光刻機。雖然,現在我們處於光刻來驅動尺寸微縮的時代,但未來驅動晶片產業繼續往前走的可能是設計與工藝協同優化,以及系統與工藝協同優化的階段。那麼,先進封裝或是下一次晶片產業洗牌的開端,中國的自主高端晶片的機會也必蘊含其中。

(本文經合作夥伴 品玩 授權轉載,並同意 TechOrange 編寫導讀與修訂標題,原文標題為〈先进封装未来将变得和光刻机一样重要?〉。首圖來源:Pxhere)